**History of Computing**

## Raúl Rojas

# Konrad Zuse's Early Computers The Quest for the Computer in Germany

## **History of Computing**

## **Founding Editor**

Martin Campbell-Kelly

### **Series Editor**

Gerard Alberts, Institute for Mathematics, University of Amsterdam, Amsterdam, The Netherlands

## **Advisory Editors**

Gerardo Con Diaz, University of California, Davis, CA, USA Jack Copeland, University of Canterbury, Christchurch, New Zealand Ulf Hashagen, Deutsches Museum, München, Germany Valérie Schafer, ISCC, CNRS, Paris, France

John V. Tucker, Department of Computer Science, Swansea University, Swansea, UK

The *History of Computing* series publishes high-quality books which address the history of computing, with an emphasis on the 'externalist' view of this history, more accessible to a wider audience. The series examines content and history from four main quadrants: the history of relevant technologies, the history of the core science, the history of relevant business and economic developments, and the history of computing as it pertains to social history and societal developments.

Titles can span a variety of product types, including but not exclusively, themed volumes, biographies, 'profile' books (with brief biographies of a number of key people), expansions of workshop proceedings, general readers, scholarly expositions, titles used as ancillary textbooks, revivals and new editions of previous worthy titles.

These books will appeal, varyingly, to academics and students in computer science, history, mathematics, business and technology studies. Some titles will also directly appeal to professionals and practitioners of different backgrounds.

Raúl Rojas

# Konrad Zuse's Early Computers

## The Quest for the Computer in Germany

Raúl Rojas Nevada, USA

ISSN 2190-6831 ISSN 2190-684X (electronic) History of Computing ISBN 978-3-031-39875-9 ISBN 978-3-031-39876-6 (eBook) https://doi.org/10.1007/978-3-031-39876-6

@ The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Switzerland AG 2023

This work is subject to copyright. All rights are solely and exclusively licensed by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

Paper in this product is recyclable.

Quando orientur controversiae, non magis disputatione opus erit inter duos philosophus, quam inter duos computistas. Sufficiet enim calamos in manus sumere sedereque ad abacos, et sibi mutuo (accito si placet amico) dicere: calculemus.<sup>1</sup>

Gottfried Wilhelm Leibniz

<sup>&</sup>lt;sup>1</sup> "If controversies were to arise, there would be no more need of disputation between two philosophers than between two calculators. For it would suffice for them to take their pencils in their hands and to sit down at the abacus, and say to each other (and if they so wish also to a friend called to help): Let us calculate."

## Foreword

This book describes the historical development of the architectures of the first computers built by the German inventor Konrad Zuse in the period 1936–1945. Although these machines are prominent in Germany, this is not the case in other countries. In many books on the history of the computer, Zuse's work receives only passing mention. However, as the various chapters in this volume show, the kind of computer architecture that Zuse developed is closer to modern computers than the architectures of the Harvard Mark I or the ENIAC, the two American machines most often celebrated as the world's first computers.

Over the years, I have published most of the material in this book as articles in academic journals, Internet sites, and conference proceedings. I started writing about Zuse's machines in 1994, so putting this book together meant reorganizing all the contributions in a coherent way. Some articles published in German have been translated for this volume. Each chapter contains references to the original publications. The advantage for the reader is that this collection brings together all stages of an amazing intellectual puzzle, the invention of the computer, no less, into a single volume.

For this book, I have chosen to keep each chapter as a stand-alone piece, so that they can be read in any order. Sufficient redundancy has been provided with explanations at the beginning of each chapter to ensure clarity of context. The reader can think of this book as a collection of essays that, after thirty years of research, are now closely interwoven.

To make the book easier to read, the preface has been written as a kind of "executive summary" containing the most important general information and chronology. It is intended for the super-busy reader. Then, for those who are just busy, the first chapter gives a comprehensive overview of the computers Zuse built from 1936 to 1945, that is, the Z1, Z2, Z3, and Z4, as well as other more specialized machines. Subsequent chapters deal with the architecture of each computer, culminating in the description of Plankalkül, the first proposal for a high-level programming language.

It is my sincere hope that the curious reader will venture out and peruse the entire book. Some chapters are easier to understand than others. For example, the Z1 computer, the mechanical calculator, is more difficult to digest than the relay machines, the Z3 or Z4. After the overview in Chap. 1, the reader can skip to the chapters on the Z3 or Z4 if she or he prefers, and then return to the chapter on the Z1. Chapter 2 is easy to follow: it describes the historical circumstances for the development of electronic computers in the USA and Europe.

This book is for the curious and the adventurous. Students and practitioners of computer science should have no trouble following the material in all chapters. Readers from other disciplines can certainly get the main message, perhaps by adopting the nonlinear reading strategy mentioned above. Start with the concise summary that follows, and you will be well on your way to retracing the steps of a remarkable intellectual adventure.

Reno, USA August 2023 Raúl Rojas

## Preface

Konrad Ernst Otto Zuse was born in Berlin in 1910 as the son of Emil and Maria Zuse. He is generally considered the father of the computer in Germany. He started thinking about automating computations as a student in the mid-1930s and built a mechanical computer from 1936 to 1938/1939. The machine was called V1 (*Versuchsmodell 1*, i.e. Experimental Model 1). By the end of the war, he had built three more important computers: the V2, V3, and V4. The four were renamed Z1, Z2, Z3, and Z4 to avoid any association with Wernher von Braun's V2 rockets. While the Z1 was a purely mechanical device (based on what Zuse called "mechanical relays"), the processor logic of the Z2, Z3, and Z4 still used sliding metal components as two-state memory elements. The logic design of all four machines was completely binary: the decimal input was converted to base two for all internal calculations in the processor. The result was converted back to decimal for display (except in the Z2, which displayed the result as 16 bits).

The Zuse machines Z1, Z3, and Z4 used the floating-point representation, where numbers are stored as a binary mantissa with its sign and an exponent of base two (for example,  $+1.010 \times 2^3$ ). The Z2 transitional machine was a fixed-point prototype, a proof of concept. All four computers had a processor, a memory, an input keyboard, and a visual display for results. Programs were punched, instruction by instruction, on 35 mm film tape. The processor of the Z1 could perform the four basic arithmetic operations, the Z2 only a subset. The Z3 could also extract square roots of numbers. The Z4 had a much larger instruction set than any of the other machines.

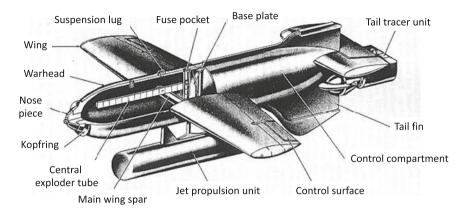

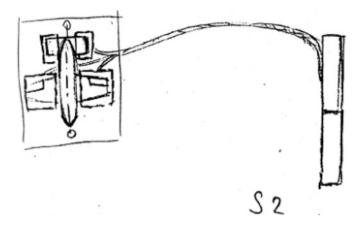

Zuse was drafted twice during the war. On both occasions, he was able to get his discharge from the front so that he could work on structural analysis for the Henschel Flugzeug-Werke, while at the same time continuing to build his calculating machines through his own company. He built two small special machines for the military (called S1, in 1942, and S2, in 1943/1944), which executed a hardwired program that calculated the appropriate profile corrections for the wings of flying bombs (Zuse was in charge of these computations at the Henschel factory in Berlin). Both machines were binary and used fixed-point numbers.

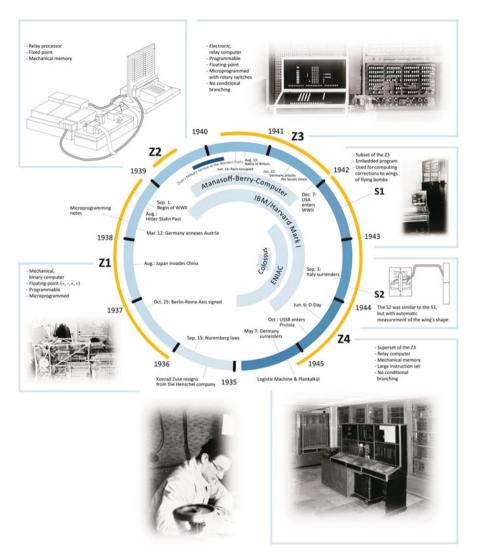

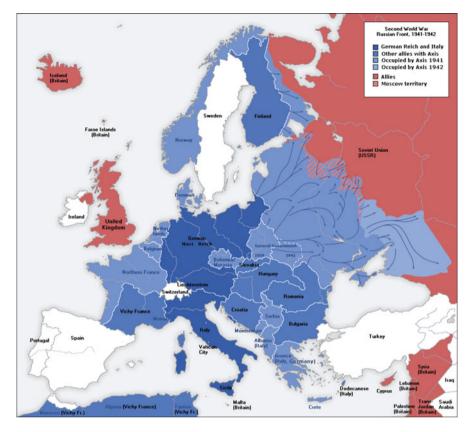

Chronology of Zuse's computers and important events during World War II

In 1941, after successfully demonstrating the Z3 relay machine computing determinants, Zuse's company received first a loan and then a military contract to supply Henschel with the Z4, a machine that would be faster, have a larger instruction set, and several punched tape readers, one for the main program and the others for program libraries. The Z4 was nearing completion by the end of the war but remained in storage for several years after the surrender. Finally, it was refurbished and leased to the ETH Zurich in 1949–1950. This concludes the early history of Zuse's computers. With this successful transaction, Zuse was able to

restart his company, the first computer start-up in Germany. The figure above shows the chronology of Zuse's early computers and how it corresponds to important events during the war. The diagram also shows the overlapping development of three important American computers and Colossus, a British war effort.

The ten years of Zuse's *Sturm und Drang* period (1935–1945) end with two theoretical results: the design of the so-called logistic machine and its profound relationship to the programming language "Plankalkül", the first high-level computer language ever proposed.

Photograph of Konrad Zuse working on the computer Z4 (Image: Konrad Zuse Internet Archive, http://zuse.zib.de/)

In this book, we follow the development of Zuse's ideas, computer by computer, explaining their architectures and capabilities. As we will see, the main weakness of all the machines was the omission of the conditional jump in the instruction set. Even the Z4, the improved and more sophisticated computer, did not have a conditional jump until the ETH required its inclusion as a prerequisite for acquiring the machine. Until then, Zuse's computers could only perform long sequences of forward calculations, or a single loop obtained by attaching the beginning and end of a punched tape. The conditional jump instruction greatly expanded the Z4's

usefulness for complex numerical calculations. Zuse stated in later years that he was aware of the need for a conditional jump, and even indirect addressing, but that both required the program to be stored in memory in order to be effective (Zuse, 1972). However, given the small size of the mechanical and electromagnetic storage units in his computers, storing the program in memory was out of the question.

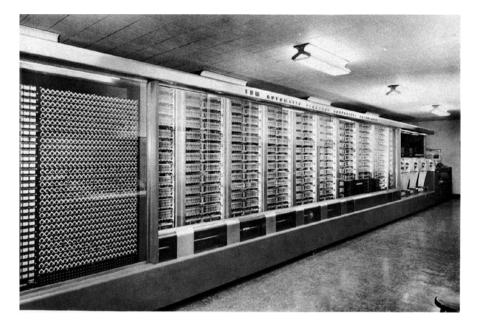

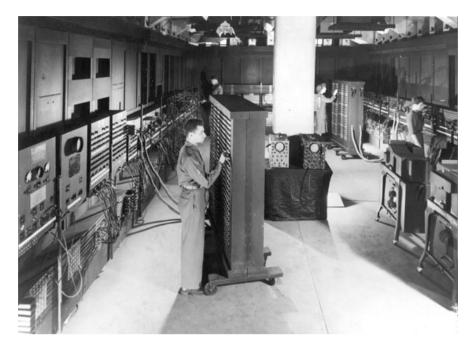

Zuse's competition in the USA was represented by three machines at this time: the Atanasoff-Berry computer, a special-purpose binary device for solving systems of linear equations, the IBM/Harvard-Mark I, a massive relay machine unveiled in 1944, and the ENIAC, the first programmable vacuum tube computer, completed in 1945 (Bruderer, 2020). As you can see from the chronology in the figure, Zuse was the early pacesetter for these developments. The Z1 was completed before the American computers were even designed. However, all three American computers could be shown to work before the Z4 was completed. Zuse's initial advantage dissipated during the war.

The Z4 was the computer that Zuse had dreamed of in 1935. Its realization took ten years of intensive work under difficult wartime conditions. The design of Plankalkül crowns these ten years, the most creative of Zuse's life. Plankalkül was a remarkable achievement because it aimed to establish a comprehensive symbolic calculus for computer programs. Consequently, Zuse devised a notation capable of expressing both predicate calculus formulas and equivalent imperative programs. In this sense, Plankalkül is both a logical specification language and an algorithmic language. Using Plankalkül notation, Zuse created the first symbolic processing programs.

It would be another five years after the war before Zuse was able to lease/sell the Z4 to the ETH, but by then the inventor who had designed all of his computers single-handedly had become an entrepreneur, and new machines were increasingly developed by committee in collaboration with his team of engineers. Zuse's company, which was re-established in 1949, operated independently until 1964, when it was acquired by Brown, Boveri & Co. Siemens bought 70% of the company in 1967 and the rest two years later. When it was liquidated in 1969, Zuse KG had delivered 251 computers in Germany and other European countries during its twenty years of operation.

Paradoxically, as late as 1950, when all new computer prototypes in other countries were electronic, Zuse was still thinking about mechanical binary components as low-cost substitutes for relays or expensive electronic tubes. He was certainly the last great maestro of mechanical computers, in the tradition of Babbage's Analytical Engine, but also one of the first builders of electromagnetic computers in the world. His pioneering achievements lie between two intellectual and technological eras, in the transition from the second to the third industrial revolution.

Nevada, USA August 2023 Raúl Rojas

## References

- Bruderer, H. 2020. *Milestones in analog and digital computing*, vol. 1 and 2, 2075 p., 3rd edn. Cham: Springer Nature Switzerland. https://doi.org/10.1007/978-3-030-40974-6.

- Zuse, K. 1972. *Der Plankalkül*, vol. 63. Sankt Augustin: Berichte der Gesellschaft für Mathematik und Datenverarbeitung.

## Acknowledgements

As with any project that has taken so long, there are many people to thank for their help and support over the years. First and foremost, I am deeply grateful to Konrad Zuse, whose generosity in sharing his knowledge and experience was instrumental in the development of this work. He was already the *grand seigneur* of computing in Germany, yet he was always interested in engaging with young researchers. Unfortunately, he passed away before our first simulation of the Z3 for the Internet was completed. It would have given him a great deal of satisfaction to see his machine running in the first Internet browsers.

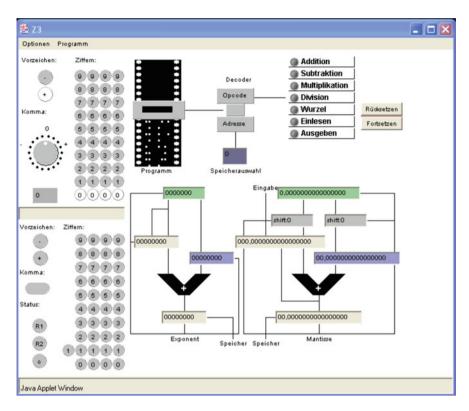

My student Alexander Thurm wrote the first Java simulation of the Z3 almost 30 years ago. My colleagues Georg Heyne and Frank Darius were the hearts and minds behind the reconstruction of the Z3 with modern relays. Our first Zuserelated project was to build a modern relay version of the addition/subtraction unit of the Z3. Thorsten Vetter, Wolfram Däumel, Lothar Schönbein, and Peter Zielske developed different parts of the electronics for both projects. Cüneyt Göktekin wrote the user interface for the Z3 reconstruction. He and Gerald Friedland as well as Lars Knipping developed important parts of the Plankalkül interpreter. Mike Krüger, Olaf Langmack, and Denis Kuniß developed the parser and executable code generator for the interpreter. Ludmila Scharf translated Zuse's chess code into Java for an Internet simulation. Hadwig Dorsch provided me with important documents and blueprints of the reconstructed Z1 built for the German Museum of Technology in Berlin. She and Eva Kudrass also gave us direct access to the machine, a rare privilege in a museum.

I must also thank Horst Zuse, Konrad Zuse's eldest son, who over the years has provided insight and support for all of our Zuse projects at Freie Universität Berlin. He was able to raise the entire funding for our reconstruction of Z3. The Konrad Zuse Society was always interested in my research and organized talks on some of the papers that are now chapters of the book.

For many years, the Konrad Zuse Center in Berlin has generously provided the server for hosting all documents in the Zuse Internet Archive, initiated by me and funded by by the German Research Foundation (DFG), as well as the simulations of Z1 and Z3. Unfortunately, the development of Java made our applets obsolete. I

Acknowledgements

would also like to acknowledge the fruitful collaboration with Dr. Wilhelm Füßl of Deutsches Museum in Munich during the successful digitization of Zuse's *Nachlass*. Special thanks to Susanne Schöttker-Söhl for her transcription work on the documents and her contributions to the digitization process.

I would like to thank friends and colleagues who provided valuable feedback and suggestions during the development of this book: Victor Perez Abreu, Rafael Gamboa, Alexander Förster, Michael Engel, David Hemmendinger, Stefan Höltgen, and Eva Kudrass for their suggestions and corrections. I am especially indebted to Prof. Wolfgang Bibel for his assistance in debugging the manuscript and for helping me to clarify the historical achievements contained in Plankalkül. His guidance and expertise were instrumental in ensuring the accuracy and clarity of the content. I would also like to thank Günter Feuer for his meticulous reading of the various chapters. His careful attention to detail and astute suggestions for deletions and consolidations greatly improved the overall readability of the manuscript. I am also grateful to Sarah Hiller for her work in cleaning up the LaTeX code and organizing the references in the book. Philomena Maher read the manuscript and corrected my English. My thanks to all of them.

I would like to express my deepest gratitude to my wife, Magui, and my daughter, Tania, for their unwavering support and understanding throughout my projects. They patiently stood by me during the long hours of work, especially during the intense periods when I was immersed in deciphering Zuse's intricate circuits. It was a challenging journey, but the ultimate satisfaction came from being able to visualize in my mind's eye the harmonious orchestration of interlocking mechanical parts within the first computer in Germany. This book is dedicated to both of them as a token of my love and gratitude.

## Contents

| 1 | Kon  | rad Zuse and the Dawn of the Computer Age                    | 1  |  |

|---|------|--------------------------------------------------------------|----|--|

|   | 1.1  | Birth and Education                                          | 1  |  |

|   | 1.2  | First Ideas: The Spreadsheet Computer                        |    |  |

|   | 1.3  | The Z1 and Z3 Machines                                       | 5  |  |

|   | 1.4  | Construction and Capabilities of the Z1, Z3, and Z4          | 8  |  |

|   | 1.5  | The Aftermath of the War and Plankalkül                      | 10 |  |

|   | 1.6  | Rebirth of Zuse's Company                                    | 13 |  |

|   | 1.7  | Epilogue                                                     | 15 |  |

|   | Refe | vrences                                                      | 16 |  |

| 2 | The  | Race to Build the Computer in World War II                   | 19 |  |

|   | 2.1  | Berlin Between the Wars                                      | 19 |  |

|   |      | 2.1.1 Science and Art in Berlin                              | 20 |  |

|   |      | 2.1.2 The Years of Computability                             | 21 |  |

|   | 2.2  | Computers in Wold War II                                     | 24 |  |

|   |      | 2.2.1 John Atanasoff's ABC                                   | 24 |  |

|   |      | 2.2.2 The Harvard Mark I                                     | 26 |  |

|   |      | 2.2.3 The ENIAC                                              | 27 |  |

|   |      | 2.2.4 Wunderwaffen and the Z4                                | 29 |  |

|   |      | 2.2.5 The First Computers                                    | 30 |  |

|   | 2.3  | Helmut Schreyer and the Electronic Computer                  | 31 |  |

|   |      | 2.3.1 The Closest Friend                                     | 32 |  |

|   |      | 2.3.2 The Electronic Computer                                | 35 |  |

|   | 2.4  | Conclusion                                                   | 37 |  |

|   | Refe | rences                                                       | 38 |  |

| 3 | The  | The Z1: Architecture and Algorithms of Zuse's First Computer |    |  |

|   | 3.1  | Konrad Zuse and the Z1                                       | 40 |  |

|   | 3.2  | Block Architecture                                           | 43 |  |

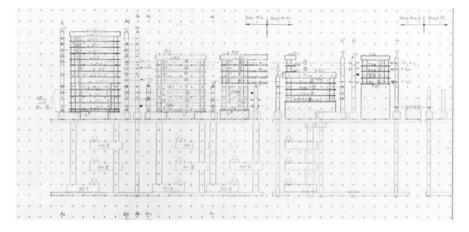

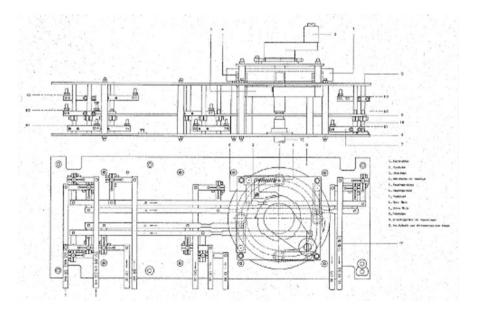

|   | 3.3  | Layout of the Mechanical Components                          |    |  |

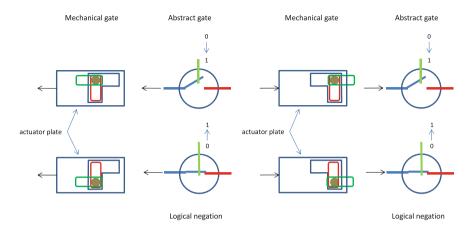

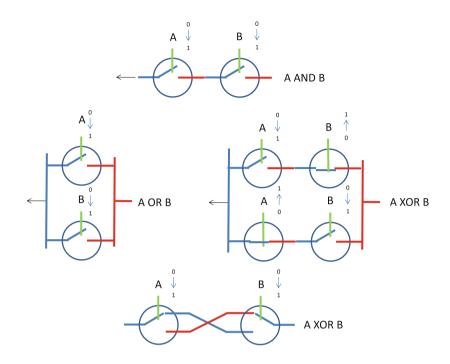

|   | 3.4  | The Mechanical Gates                                         | 49 |  |

|   |      | 3.4.1 The Mechanical Clock Cycle                             | 55 |  |

|    |                          | 3.4.2                     | Transmission of Impulses                         | 56  |  |

|----|--------------------------|---------------------------|--------------------------------------------------|-----|--|

|    |                          | 3.4.3                     | An Example: The Mechanical Addition Unit         | 57  |  |

|    |                          | 3.4.4                     | Preliminary Summary of the Mechanical Principles | 58  |  |

|    | 3.5                      | The M                     | emory of the Z1                                  | 59  |  |

|    | 3.6                      | The Ac                    | ddition Unit of the Z1                           | 60  |  |

|    | 3.7                      | The Sequencer of the Z1 6 |                                                  |     |  |

|    | 3.8                      |                           | ocessor's Datapath                               | 65  |  |

|    | 3.9                      |                           | isions                                           | 68  |  |

|    | Appe                     |                           | e Arithmetic Instructions                        | 70  |  |

|    |                          |                           |                                                  | 78  |  |

| 4  | The                      | 72 and t                  | the Cipher Machine                               | 81  |  |

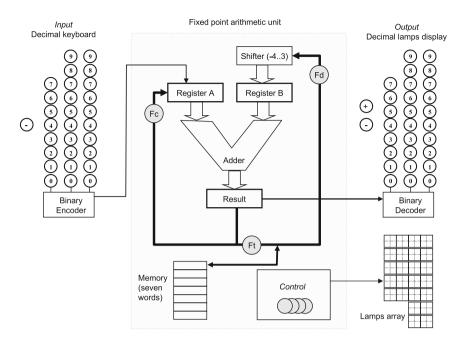

| Τ. | 4.1                      |                           | ecture of the Z2                                 | 81  |  |

|    | 4.2                      |                           | d Zuse's Proposal for a Cipher Machine           | 83  |  |

|    | 4.2                      | 4.2.1                     | The Context of the Invention                     | 83  |  |

|    |                          | 4.2.2                     | Konrad Zuse's Letter                             | 84  |  |

|    |                          | 4.2.2                     | Discussion                                       | 86  |  |

|    | Dofo                     |                           | Discussion                                       | 80  |  |

|    |                          |                           |                                                  | 07  |  |

| 5  |                          |                           | cture of the Z3                                  | 89  |  |

|    | 5.1                      |                           | Computing Machines                               | 89  |  |

|    | 5.2                      |                           | ectural Overview of the Z3                       | 91  |  |

|    |                          | 5.2.1                     | Block Structure                                  | 91  |  |

|    |                          | 5.2.2                     | Floating-Point Representation                    | 92  |  |

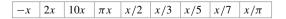

|    |                          | 5.2.3                     | Instruction Set                                  | 93  |  |

|    |                          | 5.2.4                     | Number of Cycles                                 | 93  |  |

|    |                          | 5.2.5                     | Programming Model                                | 94  |  |

|    | 5.3                      | Block                     | Diagram of the Z3                                | 96  |  |

|    |                          | 5.3.1                     | The Processor                                    | 96  |  |

|    |                          | 5.3.2                     | The Control Unit                                 | 98  |  |

|    |                          | 5.3.3                     | Microcontrol of the Z3                           | 99  |  |

|    |                          | 5.3.4                     | The Adders                                       | 100 |  |

|    | 5.4 Numerical Algorithms |                           |                                                  | 101 |  |

|    |                          | 5.4.1                     | Floating-Point Exceptions                        | 101 |  |

|    |                          | 5.4.2                     | Addition and Subtraction                         | 102 |  |

|    |                          | 5.4.3                     | Multiplication                                   | 104 |  |

|    |                          | 5.4.4                     | Division                                         | 105 |  |

|    |                          | 5.4.5                     | Square Root Extraction                           | 106 |  |

|    |                          | 5.4.6                     | Read and Display Instructions                    | 109 |  |

|    | 5.5                      | Compl                     | ete Architecture of the Z3                       | 109 |  |

|    | Refe                     |                           |                                                  | 111 |  |

| 6  | How                      | to Make                   | e Zuse's Z3 a Universal Computer                 | 113 |  |

| č  | 6.1                      |                           | sal Machines and Single Loops                    | 113 |  |

|    | 6.2                      | Simulating Branches       |                                                  |     |  |

|    | 6.3                      |                           | g the Computation                                | 116 |  |

|    |                          |                           |                                                  |     |  |

|    | 6.4   | Conclusions                                              |     |

|----|-------|----------------------------------------------------------|-----|

|    | Refer | ences                                                    | 117 |

| 7  | The S | S1 and S2: Zuse's Work for the German Military 1941–1945 | 119 |

|    | 7.1   | Introduction                                             | 119 |

|    | 7.2   | The HS-293 Flying Bomb                                   | 121 |

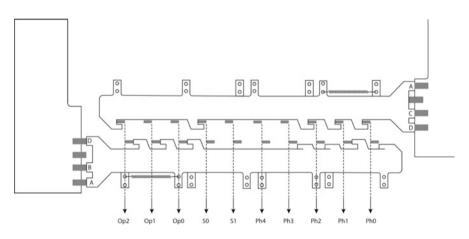

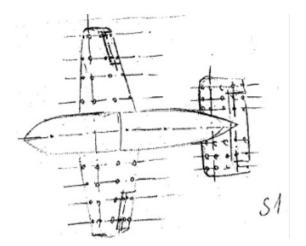

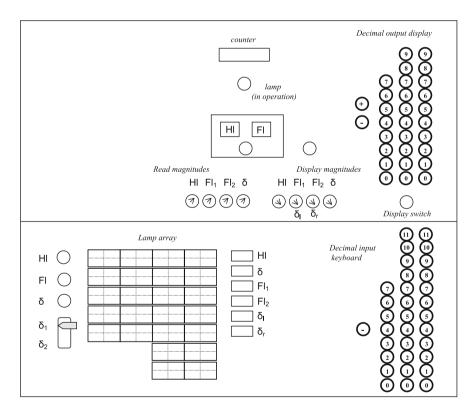

|    | 7.3   | Block Architecture of the S1                             | 124 |

|    | 7.4   | Operation of the S1                                      | 127 |

|    | 7.5   | The S2 and Automatic Process Control                     | 130 |

|    | 7.6   | Discussion                                               | 132 |

|    | Refer | ences                                                    | 133 |

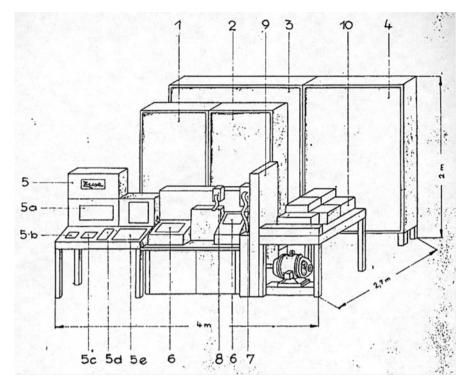

| 8  | The A | Architecture of the Z4                                   | 135 |

|    | 8.1   | Introduction                                             | 135 |

|    | 8.2   | Block Architecture                                       | 137 |

|    | 8.3   | Architectural Details                                    | 139 |

|    | 8.4   | The Arithmetic Instruction Set                           | 141 |

|    | 8.5   | Conditionals and Control Transfer                        | 143 |

|    | 8.6   | Conclusions                                              | 145 |

|    |       | ences                                                    | 146 |

| •  |       |                                                          |     |

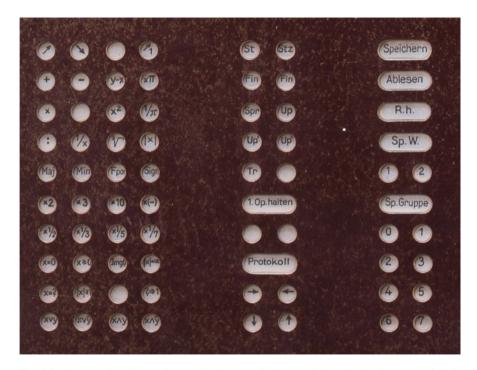

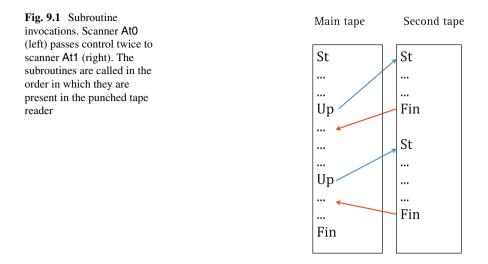

| 9  |       | Conditional Jump: Making the Z4 Universal                | 149 |

|    | 9.1   | Coding for the Z4                                        | 149 |

|    | 9.2   | The Punched Tape of the Z4                               | 150 |

|    | 9.3   | Conditional Commands                                     | 151 |

|    | 9.4   | The Conditional Jump                                     | 152 |

|    | 9.5   | The Competitors                                          | 153 |

|    | Refer | ences                                                    | 154 |

| 10 | Plan  | kalkül                                                   | 155 |

|    | 10.1  | Introduction                                             | 155 |

|    | 10.2  | Origins of the Plankalkül                                | 157 |

|    | 10.3  | Symbolic Computation                                     | 159 |

|    | 10.4  | The Syntax of the Plankalkül                             | 160 |

|    |       | 10.4.1 Variables and Data Types                          | 161 |

|    |       | 10.4.2 Arithmetic and Logic Statements                   | 163 |

|    |       | 10.4.3 Guarded Commands                                  | 164 |

|    |       | 10.4.4 Iterations                                        | 165 |

|    |       | 10.4.5 Examples of the Implicit Form of Plankalkül       | 166 |

|    |       | 10.4.6 Linearized Form of the Plankalkül                 | 168 |

|    |       | 10.4.7 Functions and Function Calls                      | 168 |

|    |       | 10.4.8 Input and Output                                  | 169 |

|    | 10.5  | Implementation Issues                                    | 170 |

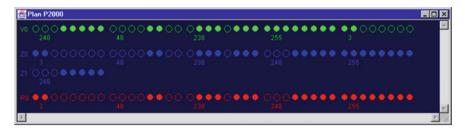

|    |       | 10.5.1 The Editor                                        | 170 |

|    |       | 10.5.2 The Parser                                        | 172 |

|    |       | 10.5.3 The Runtime System                                | 172 |

|    | 10.6  | Sample Programs                                          | 173 |

|     | 10.7         | Conclusions                                                         | 174 |

|-----|--------------|---------------------------------------------------------------------|-----|

|     | Appe         | ndix: Syntax of the Implementation of Plankalkül 2000               | 175 |

|     |              | rences                                                              | 178 |

| 11  | Zuse         | 's Computer for Binary Logic                                        | 179 |

| ••  | 11.1         | Introduction                                                        | 179 |

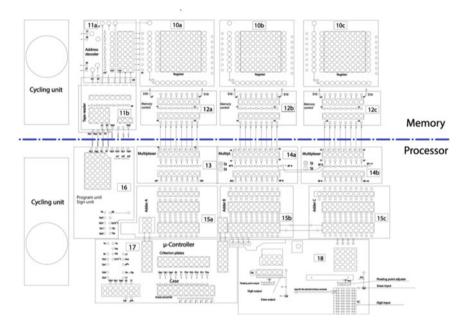

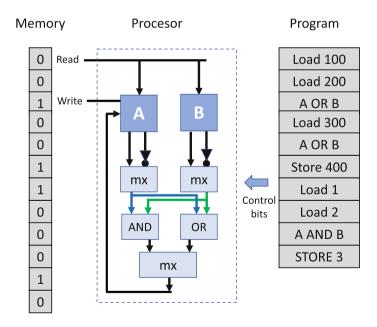

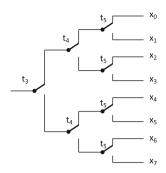

|     | 11.2         | General Structure of the Logic Machine                              | 181 |

|     | 11.2         | Encoding of the Instruction Set                                     | 183 |

|     | 11.5         | The Control and Decoding Unit                                       | 184 |

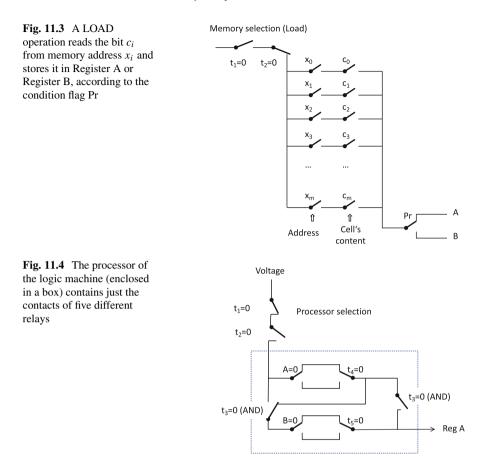

|     | 11.5         | The Memory Unit                                                     | 184 |

|     | 11.6         | The Processor                                                       | 185 |

|     | 11.7         | Was the Machine Arithmetically Complete?                            | 185 |

|     | 11.8         | Discussion                                                          | 187 |

|     |              | rences                                                              | 189 |

| 12  | The          | First Code for Computer Chess                                       | 191 |

| 14  |              |                                                                     | 191 |

|     | 12.1<br>12.2 | Computer Chess<br>Prehistory of Computer Chess                      | 191 |

|     | 12.2         | • •                                                                 | 192 |

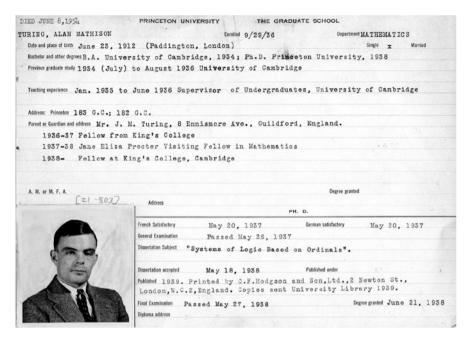

|     | 12.5         | Enter Turing                                                        | 195 |

|     | 12.4         | Zuse's Chess-Playing Program<br>Move Generation in Zuse's Notebooks | 194 |

|     | 12.5         | Computer Chess After Zuse, Turing, and Shannon                      | 197 |

|     |              | ences                                                               | 200 |

|     |              |                                                                     |     |

| 13  |              | Reconstruction of Konrad Zuse's Z3                                  | 203 |

|     | 13.1         | Introduction                                                        | 203 |

|     | 13.2         | Architecture of the Z3                                              | 205 |

|     | 13.3         | The Konrad Zuse Internet Archive                                    | 206 |

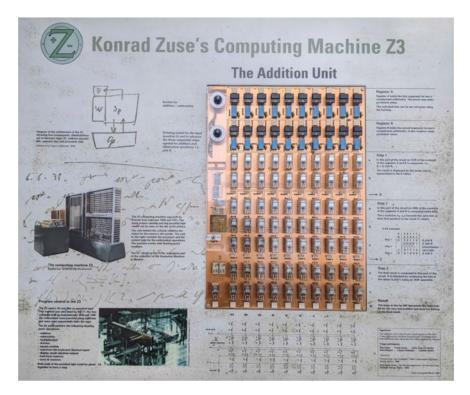

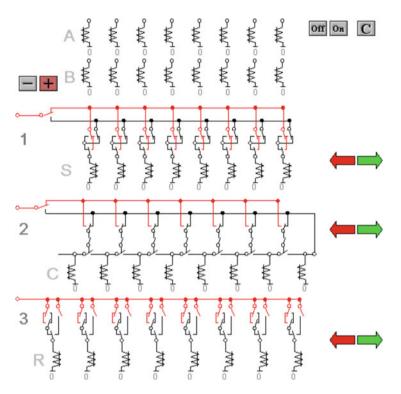

|     | 13.4         | Reconstruction of the Addition Unit                                 | 208 |

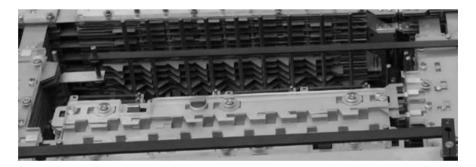

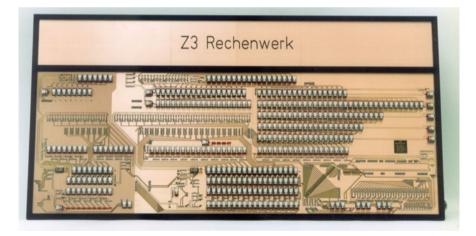

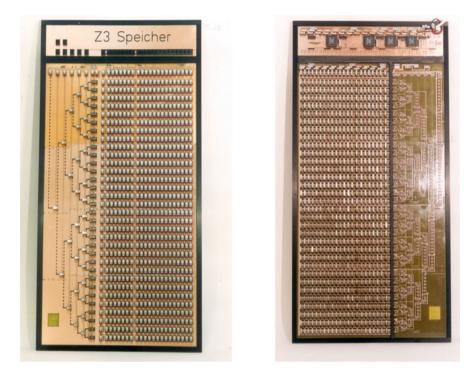

|     | 13.5         | Full Reconstruction of the Z3                                       | 210 |

|     | 13.6         | The Virtual Z3                                                      | 213 |

|     | 13.7         | Conclusions                                                         | 214 |

|     | Refe         | rences                                                              | 216 |

| 14  | Epilo        | gue                                                                 | 217 |

|     | 14.1         | A Hierarchy of Architectural Levels                                 | 218 |

|     | 14.2         | Celebrating the Z1 in 2038?                                         | 221 |

|     | 14.3         | Acknowledgments for Figures                                         | 223 |

|     | Refe         | rences                                                              | 224 |

|     |              |                                                                     |     |

| Ref | erence       | 28                                                                  | 225 |

## Chapter 1 Konrad Zuse and the Dawn of the Computer Age

This chapter provides an overview of the basic facts about Konrad Zuse and his early computing machines, i.e., those built in the period 1936–1945. The chapter summarizes the whole book.

The inventor Konrad Zuse (1910–1995) is a legendary figure in Germany, where he is widely celebrated as the "father of the computer." In 1941, Zuse unveiled the world's first programmable computing machine in his Berlin workshop. The Z3, as the machine became known, was shown to a select group of visitors to demonstrate its capabilities. Young Konrad had begun designing computers long before the war. Against all odds, he persevered during and after the global conflict.

In other countries, however, Konrad Zuse is not so well known. This is not surprising, since most of his early computers were not recognized, either in Germany or abroad, until after 1945. Many American books on the history of computing mention the German inventor only briefly (Campbell-Kelly et al. 2013). Typically, his work receives only a passing mention, even though, as this book shows, modern computers bear more resemblance to Zuse's Z1 or Z3 than to the American ENIAC or the Harvard Mark I, two other machines built during World War II.

#### **1.1 Birth and Education**

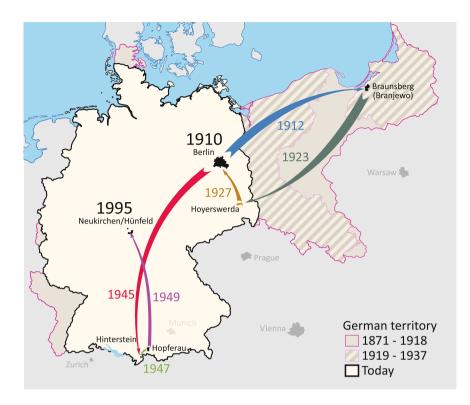

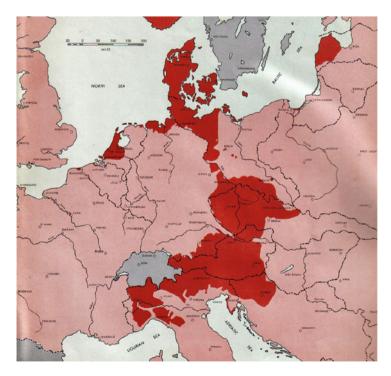

Konrad Ernst Otto Zuse was born on June 22, 1910 (2 years before the birth of Alan Turing) in Wilmersdorf, now a district of Berlin, as the son of Emil and Maria Zuse. His father was a Prussian civil servant in the postal service. Emil Zuse moved the family to Braunsberg (now Braniewo in Poland) when Konrad was 2 years old (see Fig. 1.1). Konrad attended elementary school in Braunsberg and received his basic education at the local Hosianum Gymnasium (where the famous German mathematician Karl Weierstraß had once taught). In 1923, the family moved again,

<sup>©</sup> The Author(s), under exclusive license to Springer Nature Switzerland AG 2023 R. Rojas, *Konrad Zuse's Early Computers*, History of Computing, https://doi.org/10.1007/978-3-031-39876-6\_1

**Fig. 1.1** The map of Germany after 1918 showing the location of the cities where Konrad Zuse lived and the year of migration. The shaded parts are the territories lost by Germany after World War II. The birth date is 1910, and the date of death is 1995

this time to Hoyerswerda (a town near the present-day border with Poland). Zuse was enrolled at the local *Realgymnasium*, an institution that prepared students for admission to several technical universities in Germany. In his autobiography, Zuse describes the new environment, which included a local mining industry, as better suited to his technical aspirations (Zuse 1970). It also helped that the school required fewer hours of Latin, a language Zuse detested.

In 1927, Konrad Zuse received his high school diploma (*Abitur*) and soon after began his studies at the *Technische Hochschule zu Berlin* (renamed *Technische Universität Berlin* after World War II). Zuse mentions in his memoirs that he was 2 years younger than the other students (Zuse 1970). Later in life, he regretted that he had not tried to learn more at school.

When he enrolled at the university, Zuse had not yet made up his mind about his future profession. He first tried mechanical engineering, then switched to architecture, took a year off, tried graphic design for advertising, and finally, chose civil engineering. Zuse wrote that he eventually discovered that this type of profession was ideal for him because it allowed him to combine his artistic interests with his technical skills, especially in mechanical design. It was also a profession that gave the student more creative freedom (Zuse 1972). As a high school student, Zuse was already a technical dreamer and tinkerer, often retreating to work with his "Stabil" mechanical set (a kind of German Meccano), which allowed him to build prototypes of complex machines. As a student, he won several prizes for his Stabil constructions (the last in 1928), which he liked to show off to his friends (Rojas 2001).

#### **1.2 First Ideas: The Spreadsheet Computer**

While studying civil engineering at the TH Berlin, Zuse learned to perform highly repetitive structural calculations, such as those needed to determine the stress on structures like bridges or cranes. These calculations were typically performed manually or with the aid of desk calculators. Spreadsheets with all the necessary formulas preprinted on them were painstakingly filled out, row by row, column by column. It was a tedious and repetitive task that led Zuse to consider the possibility of automating this work. In these spreadsheets, the engineer simply had to enter data and follow a fixed computational path. Therefore, he thought, a machine could take over (Kurrer 2010).

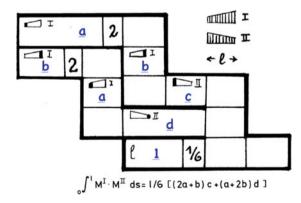

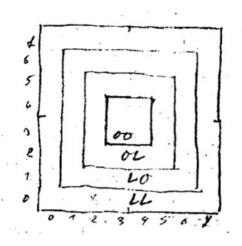

In his autobiography, Zuse traces his interest in computing machines back to 1934/35. In 1934, he submitted a "Studienarbeit" on the systematic arrangement of computations for structural analysis (Fig. 1.2) (Kurrer 2010). By then, he was thinking full-time about automating computational tasks. His initial concept was to map spreadsheets onto a plane of memory cells. In each cell, it would be possible

Fig. 1.2 Example of a spreadsheet for a static forces calculation (Zuse 1970). Numbers in cells are multiplied horizontally and added vertically, until the lowest right cell has been filled. The initial constants (in this case a, b, c, d) are written in the cells containing a symbol. That initial data trigger the subsequent computations. The final result, corresponding to the formula at the bottom, is written in the lowest cell to the right

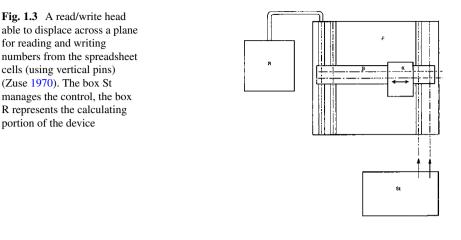

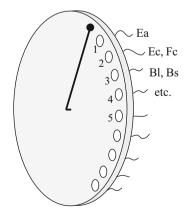

to store a number using vertical pins representing zeros or ones according to their height. A mechanical device would traverse the entire plane (using something like the mechanism of a modern xy plotter) and would be able to read numbers from each cell (encoded using vertical pins) for the computations needed in the spreadsheet (Fig. 1.3). It could then store the result in a new cell. The device would be something like a pocket calculator, but with a mobile read/write head going from cell to cell in the planar spreadsheet (Zuse 1970).

The "spreadsheet computer" envisioned by Zuse already contained some interesting ideas. One was to use the binary system to represent positive numbers, the other to represent negative numbers using the complement representation, so that subtraction could be treated as addition with a complementary number. Zuse quickly realized that the memory cells did not have to be arranged in any particular order, as they were in the spreadsheets. If the cells were numbered (i.e., addressable), they could be retrieved by their address. So he went on to design a computer with a processor and addressable memory based on binary numbers and their complement (the two's complement representation). Also during these years, he developed what he called the "semi-logarithmic" (i.e., floating-point) representation that he would use in all of his early computers. He also wrote a complete description of the binary system and the algorithms he intended to use (Zuse 1937).

We show in this book that Konrad Zuse pursued almost the same basic computer architecture during the period 1936–1945, through different incarnations of the basic ideas. His successive machines were called V1, V2, V3, and V4, with the capital V standing for Versuchsmodell (experimental model). The V was changed to Z after the war to avoid any association with the V2 rockets. Between the Z3 and Z4, Zuse built two specialized machines for the German military, the S1 and S2. The S stands for "Sondermaschine" (special machine). The S1 and S2 were based on a small subset of the Z3 architecture, but worked with fixed-point numbers (integers).

portion of the device

## 1.3 The Z1 and Z3 Machines

In July 1935, right after graduation, Zuse began working as a stress analyst for the aircraft manufacturer Henschel-Flugzeug-Werke. The German aircraft industry was expanding at a furious pace, in violation of the Versailles Peace Treaty. Only 2 years earlier, Adolf Hitler had been elected chancellor, assuming dictatorial powers, and the country was on the brink of war. Zuse's work at Henschel consisted of supervising the structural calculations needed to correct the wings of aircraft with a full metal fuselage.

Zuse remained in his position at Henschel for less than a year before resigning on May 31, 1936, in order to found his own company, which would be based on his design for a computing device. In early 1936, shortly before his departure, he wrote a lengthy memo entitled "Computing Machine for the Engineer" (Zuse 1936d) in which he detailed his vision of an automatic device comprising storage and processing components capable of performing extended sequences of basic arithmetic operations. Paradoxically, Zuse's brief tenure at Henschel would prove crucial for him in the years to come. Twice in his life, his superiors at the armament company helped him secure a discharge from the army, arguing both times that he was needed as an engineer, not on the battlefield.

In mid-1936, with the financial support of his parents, Zuse began building the automaton that had existed only in his notebooks. Some friends at the university helped by working for him, while others offered small monetary contributions so that he could finish what would become the Z1 machine. In 1937, he showed his machine to Kurt Pannke, a designer of special calculators (Zuse 1970), who was impressed enough to contribute 7000 Reichsmark for further development of the machine (at that time, a house on the outskirts of the city could be bought for 30,000 Reichsmark).

Pannke's financial support notwithstanding, one aspect that this book makes clear is that the most important difference between Zuse and other computer inventors working in the late 1930s was the fact that he was essentially building his machines alone, whereas in the United States, scientists like John Mauchly (Burks and Burks 1988) and Howard Aiken (Aiken and Hopper 1982) had the resources of universities, the military, or major corporations at their disposal. The logical and mechanical conception of the Z1 was entirely Zuse's brainchild.

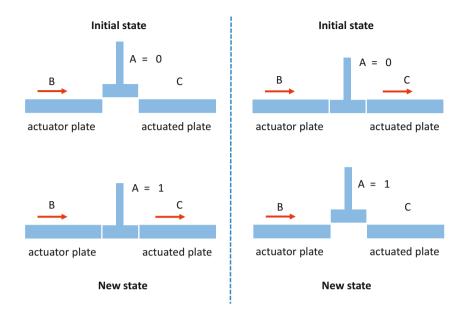

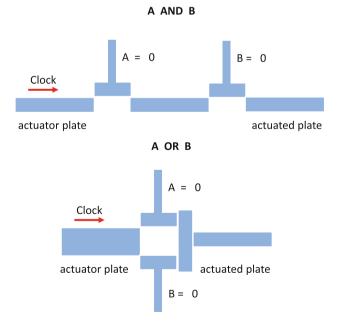

Zuse, essentially unaware of the internal structure of calculators built at the time, started from scratch and developed an entirely new type of mechanical assembly. While existing desktop calculators were based on the decimal system and used rotating mechanical components, Zuse decided to use the binary system and metal plates that could move linearly back and forth. That is, the plates could only slide from position 0 to position 1 and vice versa. Zuse's basic mechanical component was a switch that could be "opened" or "closed" like an electromagnetic relay.

Such simple mechanical elements were all that was needed for a binary machine, but important obstacles had to be overcome. It was necessary to specify the complete logical description of the machine and then "wire" it accordingly. The mechanical

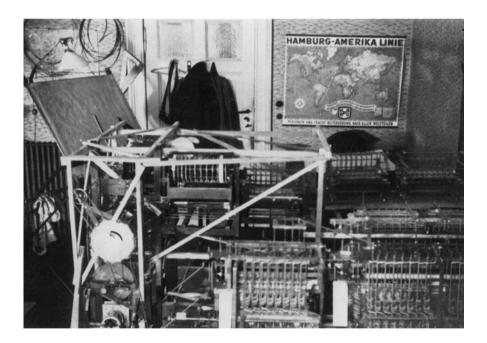

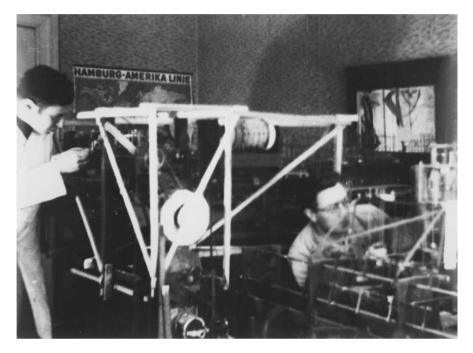

Fig. 1.4 One of the few existing pictures of the mechanical Z1 built in Zuse's living room (Image: Deutsches Museum)

components, however, posed a formidable challenge, since any movement of one logic gate had to be mechanically coupled to the movement of the other gates. Horizontal displacements of the components had to be transformed into sliding displacements over different planar layers of the machine or even into vertical movements. From today's perspective, the 3D mechanical design of the machine was much more complicated than conceiving its purely logical structure. It is fair to say that none of Zuse's friends understood exactly how the machine worked, even though they spent weeks at his home making the thousands of metal parts needed for the apparatus. One of his assistants wrote: "I am honest enough to say that I worked blind, and that I did not know how the monster that was being built there would one day work" (Zuse 1970).

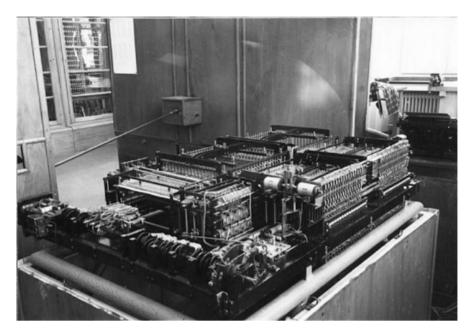

The Z1 was operational in 1938 (Fig. 1.4). It was shown to several people who saw it rattle and clatter as it computed the determinant of a  $3 \times 3$  matrix. However, the machine was never reliable enough. The mechanical components, all cut by hand from metal plates, tended to jam. Zuse later called the Z1 a "dead end." Nevertheless, the mechanical Z1 proved that the logical design was sound. An electromagnetic realization, using telephone relays, could be considered as the next step. Helmut Schreyer, an electronic engineer and college friend of Zuse, suggested the use of vacuum tubes when he saw the machine. In fact, Schreyer chose this as his dissertation project and developed some vacuum tube circuits for an electronic device. Zuse, however, doubted that vacuum tube machines could be as cheap and reliable in the long run as telephone relays or even mechanical components (Zuse

1943). Zuse's goal was to develop a robust, programmable replacement for existing mechanical calculators that could be used in large or medium-sized companies. This was to be a computing machine for the engineer, eventually small enough to be placed on a desk.

In 1938, Schreyer and Zuse showed some electronic circuits to a small group at the university. When asked how many vacuum tubes would be needed for a calculating machine, they replied that 2000 tubes and several thousand other components would be needed. The academic audience groaned in disbelief—the most complex vacuum circuits of the time contained no more than a few hundred tubes, and the electrical power required to run such a machine would be prohibitive. However, just 7 years later, ENIAC, built at the Moore School of Engineering in Philadelphia, would show the world that vacuum tube machines, while expensive, were entirely feasible (Burks and Burks 1981).

The impending invasion of Poland in 1939 had immediate consequences for Zuse: he was drafted into the army on August 26. With the help of Kurt Pannke, he tried to get a transfer to Berlin to continue his work on the next computing machine. Helmut Schreyer, who worked as an engineer at the university, also tried to get Zuse discharged by offering to build an automatic air defense system that could be operational in 2 years. His offer was met with the sardonic reply that the war would be over by then. Eventually, Zuse's acquaintances at Henschel were able to secure his discharge and transfer to the Henschel aircraft factory in Berlin-Adlershof, where he was rehired to supervise static force calculations. Later, he automated the calculations necessary to correct the wings of the "flying bombs" (radio-controlled missiles) being built at the factory.

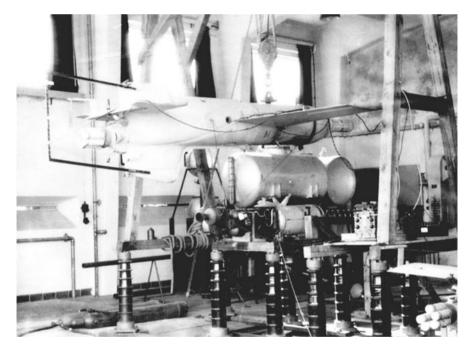

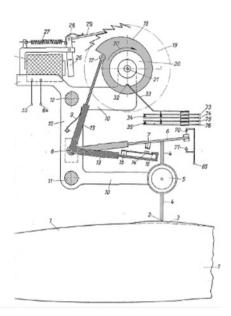

In March 1940, Zuse began working for "Special Section F" at the Henschel factory (the flying bombs unit, headed by Prof. Herbert Wagner). Two by-products of his work there were the calculating machines S1 and S2 (first named HS-1 and HS-2, where HS refers to *Henschel-Sondermaschine*). The S2 could automatically sense and measure the profile of rocket wings, convert the analog measurements into digital numbers, and compute corrections based on those values. The previous model, the S1, required manual input of these numbers using a decimal keyboard. The S1 and S2 were probably the first digital computers used for factory process control. The instrumentation used in the S2 was one of the first industrial analog-to-digital converters, although it was never used in real production. From a computational point of view, both machines were a subset of the machines described below. Their existence remained unknown to the general public for years after the war (Fig. 1.5).

In 1940, moving away from the mechanical design of the Z1, Zuse assembled the Z2 machine, an experimental prototype that used a relay-based integer processor and a mechanical memory cannibalized from the Z1. This small machine helped Zuse convince the *Deutsche Versuchsanstalt für Luftfahrt* (DVL) to partially fund the development of the Z1's successor, the Z3, which would be built using only relays.

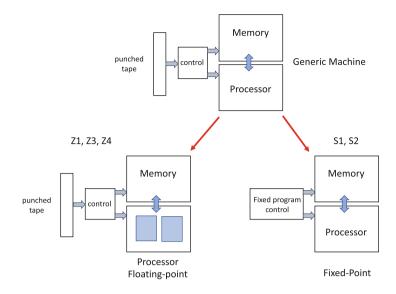

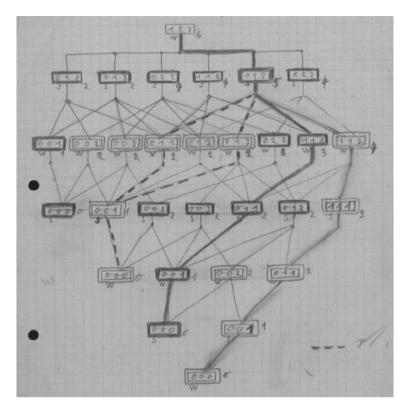

**Fig. 1.5** The abstract architecture of all Zuse's machines (on top) and its concretization in several machines that he built from 1936 to 1945. The Z1, Z3, and Z4 worked with floating-point numbers, the S1 and S2 with fixed-point numbers. The relay machine Z2 is not shown in the figure. It had the abstract structure of the Z1, but used fixed-point numbers. It was built as a proof of concept for the use of relays as binary elements

### 1.4 Construction and Capabilities of the Z1, Z3, and Z4

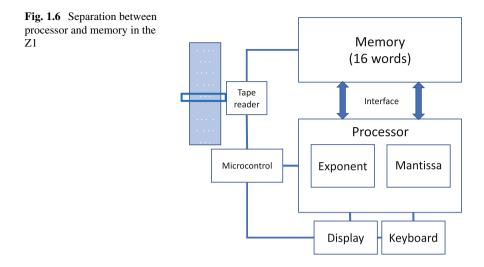

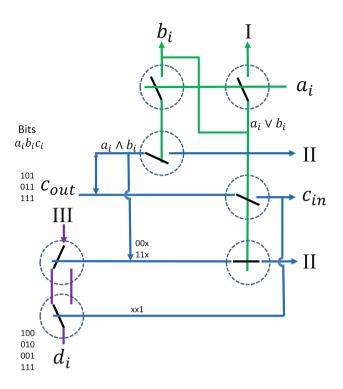

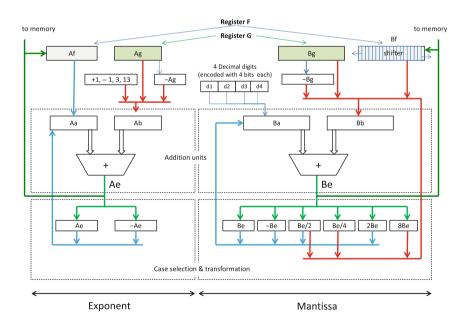

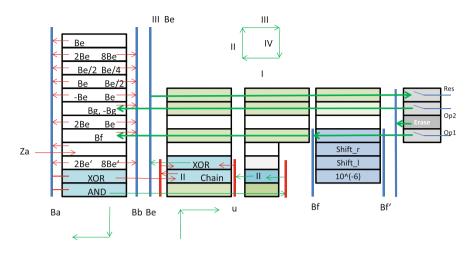

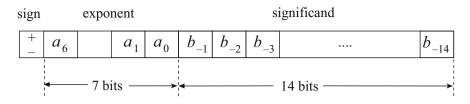

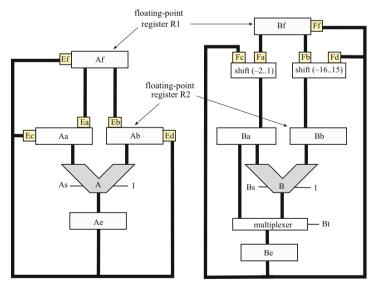

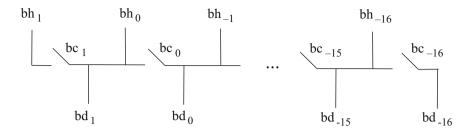

In the Z1 and Z3, the input and the results were floating-point numbers (i.e., numbers such as  $+12.654 \times 10^6$ , with an integer and a fractional part multiplying a decimal power). Zuse developed a binary representation for floating point very similar to the internal number format used in modern computers. Each number was stored in three parts: the sign of the number, the exponent of the number in two's complement notation, and the mantissa (also called the significand) of the number. To handle each part, the processor of the Z1 and Z3 consisted of two main blocks, one for processing the exponents of numbers and one for processing the mantissas (Rojas 1997). Zuse called his approach "semi-logarithmic" notation, since in the floating-point representation the exponent of base 2 represents the integer part of the logarithm (base 2) of the stored number. Zuse dated this idea to 1934 (Zuse 1972).

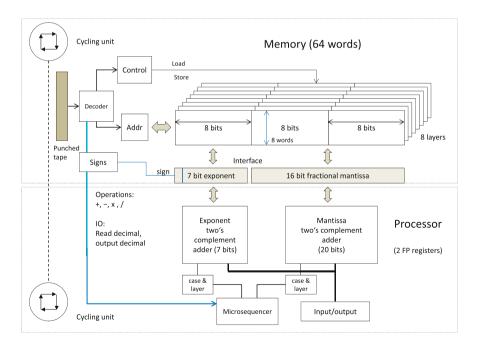

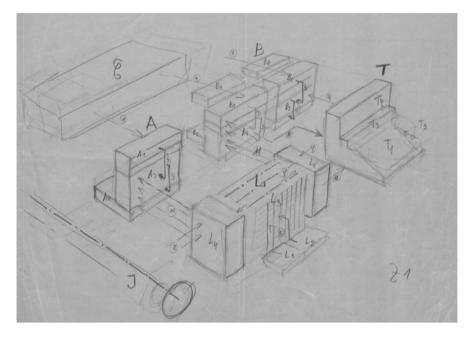

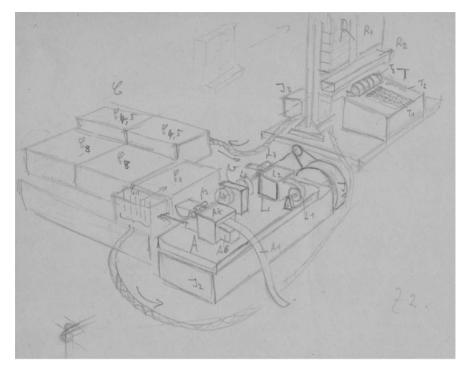

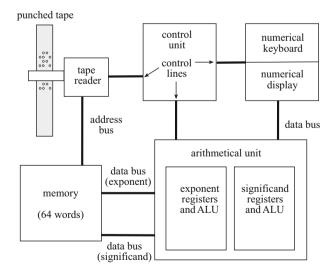

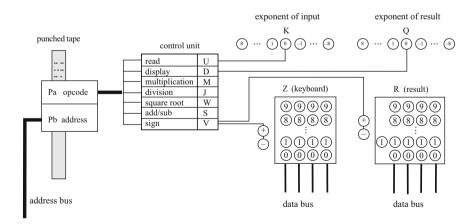

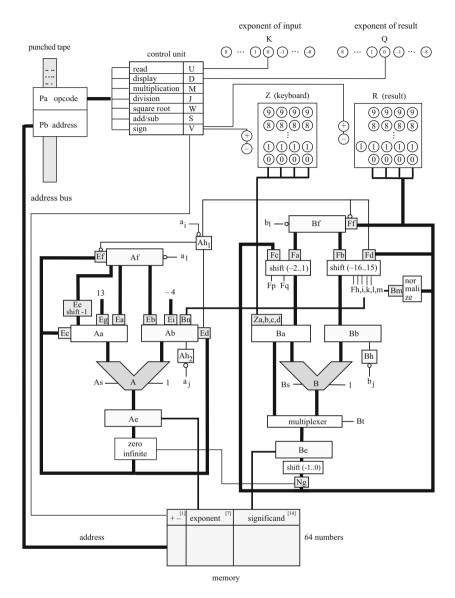

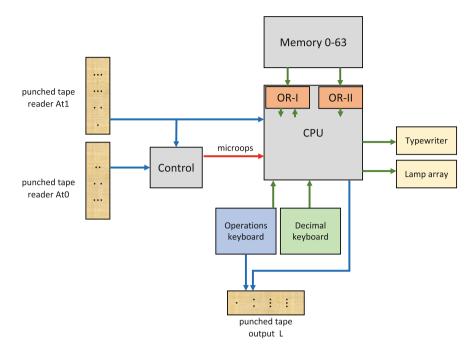

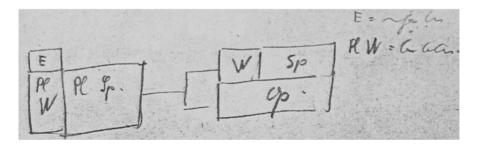

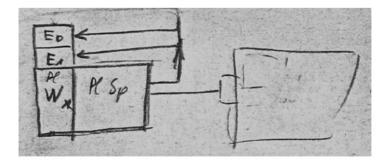

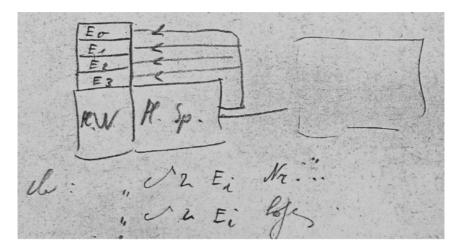

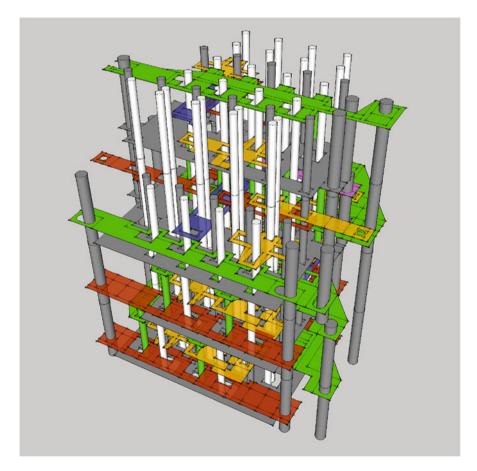

The two machines, Z1 and Z3, shared a common architecture. Their main components (Fig. 1.6) were:

- 1. The memory for storing numbers (16 in the Z1, 64 in the Z3).

- 2. The processor for performing arithmetic operations.

- 3. A punched tape for storing the sequence of program instructions.

- 4. A decimal input/output console.

Instructions were read from the tape to be executed one by one by the processor. The console allowed the user to enter decimal numbers with a decimal keyboard (similar to the keyboard of a cash register), while the results were displayed in a panel with decimal digits that were selected to be uncovered mechanically in the Z1 or highlighted with lamps in the Z3.

The instruction set of the Z1 and Z3 included the four arithmetic operations (addition, subtraction, multiplication, and division). The Z3 also included the square root operation. There were two additional operations for reading and displaying decimal results (convert from decimal to binary and vice versa) and two for transferring numbers between the processor and memory (load and store). The Z3 was very much like an early electronic calculator of the 1970s, but much slower: a multiplication had 18 machine cycles and did the calculation in 3 seconds. Division and square root operations were performed in about the same time.

With the instruction set mentioned above, it was possible to compute any arithmetic formula of the kind used in the engineering applications Zuse had in mind. However, the instruction set did not provide a conditional branch instruction, so it was relatively difficult, though not impossible, to perform conditional computations. Also, the two ends of the punched tape could be joined to form a loop, so that repeated execution of the same program was possible.

I have always thought that Zuse's vision of a spreadsheet computer, where all computations flow deterministically from start to finish, made him overlook the crucial importance of the conditional branch, even for small programs. It is possible that the static computations that Zuse had to supervise at Henschel were almost always embedded in spreadsheets. In his autobiography, Zuse explains the lack of the conditional branch as a way of keeping the complexity of the machine's computations down, but his explanation is not convincing (Zuse 1970). Zuse offers another explanation in his 1945 design for a high-level language, the Plankalkül. He

writes: "I deliberately did not include the conditional branch and the computation of addresses in the machines to be developed, because this would have delayed their delivery. Also, the necessary technical conditions were not available during those war years (for example, the construction of storage units with sufficient capacity to store the computer program)" (Zuse 1972).

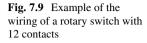

Zuse kept the number of logic gates for the processor low by relying on controllers that acted as microsequencers, one for each instruction in the instruction set. A microsequencer in the Z3 consisted of a rotating arm that advanced one step in each cycle of the machine, like a rotary dial. A motor provided the clock cycles needed to synchronize all parts of the machine. In the case of the Z3, the operating frequency was set at five cycles per second. That is, five times per second, the rotating arm in a microsequencer activated the next microstep of the current operation. For example, in the case of multiplication, repeated addition and shifting of numbers were required (as happens when you multiply two numbers by hand). The required 18 suboperations were all started by a microsequencer with 18 contacts for the rotary switch. The microsequencer can be thought of as a kind of hardwired program that reduces very complex instructions to a sequence of simple operations. Therefore, the entire internal operation of the machine could be changed by rewiring the microsequencers without having to change the rest of the processor. This resulted in a very efficient and flexible architecture and explains how Konrad Zuse was able to build a machine that rivaled the British or American computers of the same period, despite having far fewer resources at his disposal.

During World War II, Zuse worked for the Henschel factory, but was finally able to start his own business in April 1941. The *Zuse Ingenieurbüro und Apparatebau, Berlin* was the first company in the world founded with the sole purpose of developing computers. The successful demonstration of the Z3 brought Zuse a contract with the DVL and then with the Ministry of Aviation to develop an even larger computer, the Z4. This machine had a very similar design to the Z3, but with a larger instruction set. The machine was built (with an initial memory of 12 words, expandable to 64) and was almost operational by February 1945. By this time, Zuse's company already had 20 employees (Table 1.1).

#### 1.5 The Aftermath of the War and Plankalkül

In early 1945, Zuse fled with the Z4 before Berlin fell to the Soviet Army. One of his collaborators was able to get the machine shipped by train and somehow managed to misrepresent it as being of strategic military value. The Z1 and Z3 had already been destroyed in air raids 2 years earlier, leaving the Z4 as the only asset of Zuse's company. After several detours, Zuse and his team settled in Bavaria, where he survived the following years by painting postcards, consulting, and attempting to restart his company. During this period of forced inactivity, he completed his manuscript on the Plankalkül, a remarkable document first published in 1972.

| Name | Years     | Ordered by | Type              | Technology                | Status       | Status       |

|------|-----------|------------|-------------------|---------------------------|--------------|--------------|

| V1   | 1936-1938 | ,          | Algebraic         | Mechanical                | Experimental | Destroyed    |

| V2   | 1939-1940 |            | Algebraic         | Relays, mechanical memory | Experimental | Destroyed    |

| V3   | 1939-1942 | DVL        | Algebraic         | Relays, 64 memory cells   | Experimental | Destroyed    |

| V4   | 1942-1945 | RLM        | Algebraic         | Relays, mechanical memory | Commercial   | Preserved    |

| 51   | 1942      | HFW        | Special-purpose   | Relays                    | Used         | Disassembled |

| S2a  | 1943-1944 | HFW        | Special-purpose   | Relays                    | Unused       | Disassembled |

| S2b  |           | HFW        | Automatic sensing | Relays                    | Unused       | Disassembled |

| L3   | 1944      |            | Logic             | Relays                    | Theoretical  |              |

| 51   | 1940-1945 |            | RLM               | Vacuum tubes              | Experimental | Destroyed    |

| s to Henschel-Flugzeug-Werke, and RLM to           |                          |

|----------------------------------------------------|--------------------------|

| e 1946). The abbreviation HFW refer                |                          |

| the Zuse machines built from 1936 until 1945 (Zuse | istry                    |

| Table 1.1 Overview of the                          | he Reich's Aviation Mini |

The Plankalkül (calculus of programs) was the world's first high-level programming language (Zuse 1972). It was designed by Zuse between 1939 and 1945, at a time when the first computers were being built in the USA, United Kingdom, and Germany. It represents one of the most important contributions to the history of ideas in the field of computing, although it was first implemented in 1999 by our research team in Berlin.

The Plankalkül corresponds to Zuse's mature conception of how to build a computer and how to allocate the total computing work to the hardware and software of a machine. Zuse called the first computers he built "algebraic" in contrast to the "logistic machines" (Zuse 1943). The former were built specifically to handle scientific computations, while the latter could handle both scientific and symbolic processing problems. In modern computers, there are two ALUs, one for integers and one or more for floating-point operations. It would not have been impossible to do logic operations in the Z3 or Z4, but it is cumbersome to do so with floating-point registers. For Zuse, the distinction between algebraic and logical computation emphasized the need for two types of machines. In fact, in 1950, he applied for a patent for a "combined machine" with a floating-point processor and a logic processor running in parallel and with a common memory unit (Zuse 1950).

Around 1944, Zuse greatly simplified the hardware needed to perform logic operations. What he came to call the "logic machine" was never fully developed (although a small prototype was built), but his design called for a one-bit word memory and a processor that could compute only basic logic operations (conjunction, disjunction, and negation). It was a sort of minimalist computer in which the memory consisted of a long chain of bits that could be grouped in any way to represent numbers, characters, arrays, and so on. In some ways, the logistic machine resembles Alan Turing's 1936 proposal for what we now call a Turing machine.

The Plankalkül was the software counterpart of the logistic machine. Complex structures could be built as arrays of elementary ones, the simplest being a single bit. Today we would call Zuse's arrays multidimensional "tensors," but the addressing was more in the form of a tree. A matrix, for example, would be a tree with rows hanging from the root. An element in the matrix could be addressed by first specifying the row and then the element in the row.

Also, sequences of instructions could be grouped into subroutines and functions, so that the user was dealing only with a powerful high-level instruction set that masked the complexity of the underlying hardware. The Plankalkül strongly exploited the concept of modularity, so important in computer science today: multiple layers of software made the hardware invisible to the programmer. The hardware itself only had to execute a minimal set of instructions.

In Plankalkül, the programmer uses variables to store the results of computations. There are no separate variable declarations: any variable can be used in any part of the program, and its type is written along with its name. Variable assignment is done as in modern imperative programming languages, where a new value overwrites the old one. Many operations are those used in modern programming languages (addition, subtraction, etc.). Plankalkül is universal. It can handle conditional instructions of the type "IF-THEN-ELSE" and provides an iteration operator W,

which repeats the execution of a sequence of instructions until a terminal condition is met. Using these constructs, any kind of computation can be expressed with Plankalkül.

When Zuse started to develop the Plankalkül, he wanted to develop a complete "calculus of programs." In the case of algebraic expressions, he wrote, we can equate a quadratic polynomial to zero and, by applying algebraic rules, derive an explicit formula for its roots. He aspired to do the same for the predicate calculus. However, this would have involved developing automatic proof methods for general formulas of the predicate calculus, a very ambitious undertaking. In the 1972 edition of Plankalkül, Zuse wrote that solving general logic formulas "is not so easy." Consequently, this problem was not further explored in the manuscript. Nevertheless, Zuse emphasized that Plankalkül served both as a notation for describing logical concepts and as an algorithmic language capable of facilitating various computations (Zuse 1972).

Although Zuse published some small papers about the Plankalkül and tried to make it known in Germany, it never generated enough interest. The main problems were its ambitious scope, the large number of possible commands, its modular architecture requiring incremental compilation, and the presence of dynamic structures, set-theoretic operations, and functionals. Some aspects of the definition were ambiguous, and the lack of type checking would have made debugging extremely difficult. A practical implementation of Plankalkül certainly requires a major revision of Zuse's 1945 draft. However, Plankalkül was very much ahead of its time, considering that many of the concepts on which it was based would be rediscovered much later (including logic and functional programming). Decades would pass before programming languages reached the level of sophistication of Plankalkül.

#### 1.6 Rebirth of Zuse's Company

After the war, in 1947, Zuse restarted his company as *Zuse Ingenieurbüro*. It had a new lease of life when Prof. Eduard Stiefel of the *Eidgenossische Technische Hochschule* (ETH) in Zurich went to Bavaria to see the refurbished Z4 in operation. He decided to lease/buy the machine for his university. With this funding and some partners, Zuse restarted his company for the second time in 1949 as *Zuse Kommanditgesellschaft*.

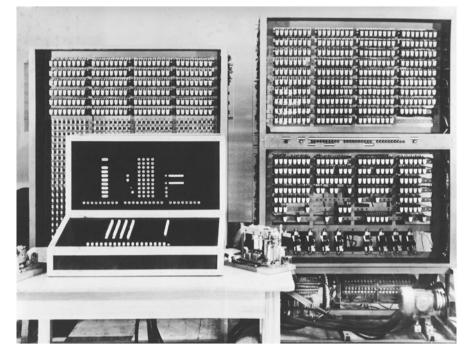

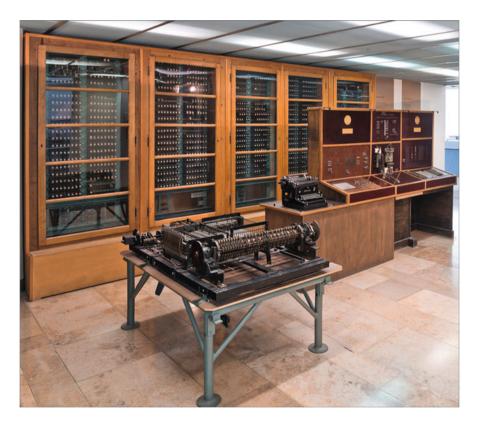

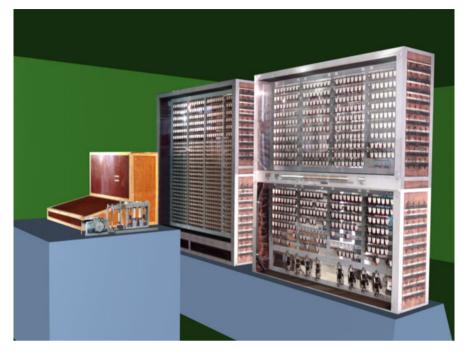

The Z4 was installed in Zurich in 1950, several months before the first UNIVAC was delivered in the United States (Stern 1981; Bruderer 2012), and was thus the first commercial computer in the world. For several years, the Z4 was also the only commercial computer installed in continental Europe. The machine had the same logical structure as the Z3, but contained more memory and an expanded instruction set. It was used at the ETH for 5 years and is now part of the historical collection of Deutsches Museum in Munich. It is the only Zuse machine built before 1945 that has survived.

Zuse's company (with the new name "Zuse KG") flourished after the war, and many more machines were built. They were all numbered progressively according to their introduction, i.e., Z5, Z11, and so on. For some years, Zuse continued to build relay computers and even advocated the use of micromechanical elements. Gradually, however, electronic components were miniaturized, their reliability increased, and with the dominance of American companies in this field, Zuse KG had no choice but to develop vacuum tube and transistor-based machines. Zuse KG's first transistorized computer was the Z23, a commercial success: 80 machines were shipped to customers in Germany and 18 to other countries. The *Deutsche Forschungsgemeinschaft* actively promoted the machine and subsidized universities that bought it. The Z23 was the computer used to start many computer science programs in Germany.

The Z23 and the Z22 (the latter built with vacuum tubes) were remarkable in that they represented the first radical departure from the architecture of all previous Zuse machines. Their internal structure consisted of serial registers, which required fewer components. The number of instructions was kept to a minimum. A compiler allowed programmers to write code with a syntax somewhere between assembly code and a high-level programming language. Machines such as the Z22 and Z23 were largely designed by Zuse's engineers.

Another important development, and Zuse's final encore, was the introduction in 1961 of the Graphomat, a plotter that could be used by architects and geologists to plot diagrams and drawings. The Graphomat could be connected to Zuse's computers and used special gears to provide smooth, continuous motion in any direction. The gears were designed by Zuse himself.

The Z23 and the Graphomat were successful, but development of the next line of computers proved too costly. Eventually, the dominance of the American computer industry in Europe, as well as the late adoption of an all-electronic design, brought Zuse KG into financial difficulties. The company accepted an industrial investor, but was later sold to Brown Boveri and Co. in 1964. Seventy percent was then sold to Siemens in 1967 and the remainder in 1969. Production of the Zuse series of computers was discontinued. Zuse retired after the Siemens takeover and received a pension. In the years that followed, he continued to write, apply for patents, and argue for his place in the history of computing.

In retrospect, it can be said that Konrad Zuse's greatest achievement was the development of a family of fully digital, floating-point, programmable machines built in almost total intellectual isolation from 1936 to 1945. His dream was to create a small computer for business and scientific applications. He worked tirelessly for many years to achieve this goal. Unfortunately, his 1941 patent application (Zuse 1941) for the Z3 computing machine was rejected by a German judge in 1967 for lack of "inventiveness." The decision on the application was delayed so long because of the war and because the major computer companies fought in court against Zuse, who always considered himself the one and only inventor of the computer. His public statements on the subject sometimes revealed some bitterness about his lack of recognition in other countries.

#### 1.7 Epilogue

Konrad Zuse married Gisela Brandes in 1945, before Berlin was under siege. Gisela gave birth to their first son a few months later, and four more children followed in the ensuing years. However, Konrad Zuse was not a family man—over the years his obsession was to build new and better machines. After his retirement, he received many honors in Germany, including the Federal Cross of Merit and the Siemens Ring. In 1999, he was named a Fellow of the Computer Museum in California. He received numerous honorary doctorates and an honorary professorship. In addition, the most important German prize in the field of computer science bears his name.

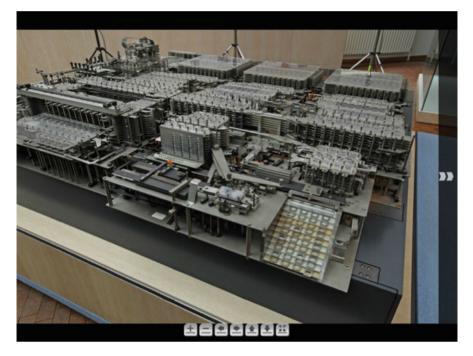

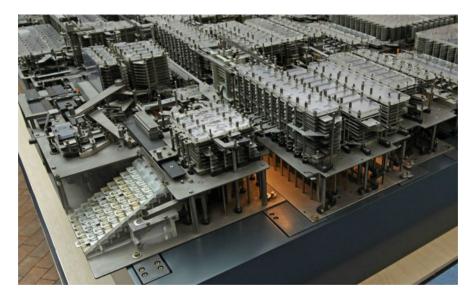

His early machines have been reconstructed: a model of the Z1 was built by Zuse himself in the 1980s and is on display at the German Museum of Technology in Berlin (Schweier and Saupe 1988). The Z3 was reconstructed by Zuse's engineers in 1960 and has been part of the historical collection of Deutsches Museum in Munich since 1969. A new functional replica of the Z3, with smaller relays, was built by us in Berlin in 2001 and is on display in the Zuse Museum in Hünfeld, Germany, which also houses several computers of the Zuse KG. Konrad Zuse's notebooks and documents were sold to Deutsches Museum in 2006, where they are now stored in the library's stacks and digital archives.

It has often been said that the computer was a by-product of World War II, or at least that its birth was catalyzed by the events surrounding the conflagration. In the case of Konrad Zuse, this is only partially true. The inspiration for his first computing machine, the Z1, predates the war. The 6 months Zuse spent at the front in 1939–1940 were certainly an interruption in the project he had been working on for almost 3 years. Without the war, the Z3 would have been finished sooner. But once the war broke out, Zuse was able to convince the military establishment that calculating machines were useful for aerodynamic calculations. The successful demonstration of the Z2 prototype led to a contract with the DVL, which financed most of the construction of the Z3. Once the Z3 was operational, Zuse developed the special-purpose machines S1 and S2 and began building the more powerful computing machine he had been dreaming of all these years, the Z4.

Although at the time almost no one in Germany fully understood the significance of Zuse's work, at least those responsible for the strategic management of aeronautical research and development recognized the importance of fast computing. It is noteworthy that Zuse was able to leave the front twice, and that he was partially relieved of his day-to-day responsibilities at Henschel-Flugzeug-Werke to take care of his own company. This would not have happened if the military experts had not thought that his commercial work was useful and necessary for the war effort.

Konrad Zuse was certainly no resistance hero, but it is true that he never sought political office or a position in the academic or industrial establishment. While professors and researchers at German universities, especially at the TH Berlin, flocked to the Nazi Party to further their careers, Zuse's own vocation was cut short by the war. Unfortunately, not much is known about his political views at the time. In his memoirs, Zuse devotes only a few paragraphs to the regime and politics during the war. Ideologically, he was very impressed by Oswald Spengler's theory of the decline of Western civilization. He continued to mention Spengler even in his later years.

It was probably Konrad Zuse's personal misfortune that he conceived all the elements of the computer earlier and more elegantly than the other computer pioneers of his time (except Turing), but that he lived in Germany when the country was on its way to a war of aggression and eventual self-destruction. Outside the country, and outside a very small circle in Berlin, no one took notice of the Z1, Z2, Z3, and Z4. The S1 and S2 were secret machines. Zuse's work was not rediscovered until the late 1940s, but it was too late for his machines to have a major impact on the design and construction of modern electronic computers. Zuse's work became, at best, a footnote in early scholarly books on the history of computing. This has changed in recent decades as more has become known about the life and work of this most remarkable computer pioneer (Bruderer 2020).

#### References

- Aiken, H.H., and G.M. Hopper. 1982. The Automatic Sequence Controlled Calculator. In *The Origins of Digital Computers, Monographs in Computer Science*, ed. B. Randell, 203–222. Berlin: Springer. https://doi.org/10.1109/EE.1946.6434251.

- Bruderer, H. 2012. Konrad Zuse und die Schweiz: Wer hat den Computer erfunden? Munich: Oldenbourg Wissenschaftsverlag. https://doi.org/10.1524/9783486716658.

- Bruderer, H. 2020. *Milestones in Analog and Digital Computing*. Vols. 1 and 2, 3rd ed., 2075. Cham: Springer Nature Switzerland. https://doi.org/10.1007/978-3-030-40974-6.

- Burks, A.W., and A.R. Burks. 1981. The ENIAC: First General-Purpose Electronic Computer. Annals of the History of Computing 3 (4): 310–399, https://doi.org/10.1109/MAHC.1981. 10043.

- Burks, A.R., and A.W. Burks. 1988. *The First Electronic Computer The Atanasoff Story*. Ann Arbor: The University of Michigan Press.

- Campbell-Kelly, M., W. Aspray, N. Ensmenger, and J.R. Yost. 2013. Computer: A History of the Information Machine. 3rd ed. The Sloan Technology Series. https://doi.org/10.4324/ 9780429495373.

- Kurrer, K.E. 2010. Konrad Zuse und die Baustatik Zur Vorgeschichte der Computerstatik (Teil I). Bautechnik 87 (11). https://doi.org/10.1002/bate.201010046

- Rojas, R. 1997. Konrad Zuse's Legacy: The Architecture of the Z1 and Z3. IEEE Annals of the History of Computing 19 (2): 5–16. https://doi.org/10.1109/85.586067.

- Rojas, R. 2001. Konrad Zuse War der Erfinder des Computers doch kein Musterschüler? Telepolis.de

- Schweier, U., and D. Saupe. 1988. Funktions- und Konstruktionsprinzipien der Programmgesteuerten Rechenmaschine "Z1". Arbeitspapiere der Gesellschaft für Mathematik und Datenverarbeitung 321.

- Stern, N. 1981. From ENIAC to UNIVAC. Bedford: Digital Press.

- Zuse, K. 1936. Die Rechenmaschine des Ingenieurs. Deutsches Museum Digital. http://digital. deutsches-museum.de/item/NL-207-0209/.

- Zuse, K. 1936d. Patentanmeldung Z 23 139 IX / 42m: Verfahren zur selbsttätigen Durchführung von Rechnungen mit Hilfe von Rechenmaschinen [für Zuse]. Deutsches Museum Digital. http://digital.deutsches-museum.de/item/NL-207-0990/.

- Zuse, K. 1937. Einführung in die allgemeine Dyadik. Deutsches Museum Digital. http://digital. deutsches-museum.de/item/NL-207-0210/.

- Zuse, K. 1941. Patentanmeldung Z-391. German Patent Office, Berlin.

- Zuse, K. 1943. Rechenplangesteuerte Rechengeräte für technische und wissenschaftliche Rechnungen. Deutsches Museum Digital. http://digital.deutsches-museum.de/item/NL-207-0217/.

- Zuse, K. 1946. Zur Entwicklung von Rechengeräten bis zum Jahre 1945. Nennung von Namen und finanziellen Unterstützungen. Available online at the Zuse Internet Archive.

- Zuse, K. 1950. Patentschrift Nr.926449, Kombinierte numerische und nichtnumerische Rechenmaschine. Deutsches Patentamt, 11 Seiten.

- Zuse, K. 1970. Der Computer Mein Lebenswerk. Landsberg: Verlag Moderne Industrie,

- Zuse, K. 1972. Der Plankalkül. 63, Berichte der Gesellschaft für Mathematik und Datenverarbeitung, Sankt Augustin.

# **Chapter 2 The Race to Build the Computer in World War II**

This chapter traces the invention of the computer in several countries during the interwar period and up to 1945, concentrating on events in Germany and comparing Zuse's machines with those invented in the USA. In the second part, we look at Helmut Schreyer's electronic prototype and some aspects of his life and work during the Second World War.

## 2.1 Berlin Between the Wars

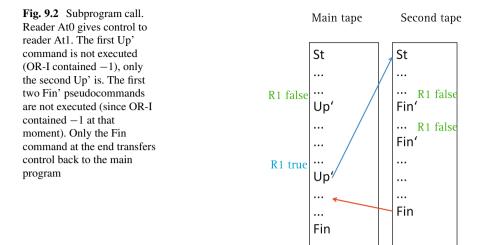

The armistice between the Entente powers and Germany was signed on November 11, 1918, effectively ending the First World War with the defeat of Germany. The peace document, the Treaty of Versailles, was signed a year later on June 28. But after 4 years of war, Germany could not be stabilized. Peace in Europe did not mean peace within Germany itself. It would only be 20 years before most of Europe was engulfed in the continuation of the war.